摘要:设计了多通道高速遥测采编器,主要完成对飞行器工作的复杂环境参数的 32 路模拟量采集和实时显示。系统采用一片 ADC 分时复用方式,采集数据使用数字滤波 -FIR 滤波处理,很好的滤除白噪声干扰。ADC 选用 AD9220,其最大采样率为 10Msps,与上位机通信电路采用 USB 接口芯片的 FT232H,其异步 FIFO 模式最高速率可达 8Mbps 的传输速率,同时通过工业 IOCOMP 控件快速绘制实时曲线,避免了采用 Line 函数绘制曲线的延时问题,实用于高速的数据采集系统。此设计方案可作为一种通用型数据采集系统,适用于不同采样要求。

关键词: 采编器; FIR 滤波; IOCOMP 控件; AD9220; FT232H

中图分类号: TP274<sup>+</sup>.7 文献标识码: B 文章编号: 1006-883X (2015) 02-0039-06 收稿日期: 2014-12-08

## 多通道高速遥测采编器的设计

李晓红

太原工业学院 电子工程系, 山西 太原 030051

#### 一、引言

速数据采集技术广泛应用于智能仪器、信号处理及工业自动控制等领域,主要完成对信息(温度,压力,流量,位移以及角度等)数据的采集和存储控制等功能<sup>[1]</sup>。制约系统高速的因素有 ADC 采样率、信号传输速率及绘制显示曲线速度等。

本文设计的多通道高速遥测采编器主要实现 32 路 速变飞行器环境参数的采集、信号处理及实时显示。

系统为配置灵活性,采用 FPGA 自带 FIR IP 核实现数字滤波,其优点是实现简单、处理速度快与上位机的通信接口采用 USB 接口,可快速上传采集数据。此外,本文运用 IOCOMP 工业控件组件可快速实现数据波形的显示,美观且操作简单 $^{\Pi}$ 。

#### 二、设计方案

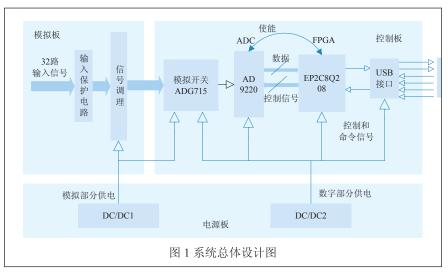

系统总体设计图如图 1 所示,32 路信号输入后首先经过信号输入保护电路与信号调理。 调理电路包括信号低通滤波、电压跟随等。同时对模拟电路与数字电路进行分开供电,这样 保证信号的稳定,避免数字信号对模拟信号的干扰噪声。ADC采用AD公司的AD9220,与两片模拟开关ADG715配合可完成32通道的信号采集;控制器为Altera公司的EP2C8Q208。考虑到FPGA内部的存储容量较大,在实现与USB通信时使用其内部FIFO完成数据缓冲,节约硬件成本与简化PCB布线;USB接口芯片选用FTDI公司的第6代产品FT232H,其全速为12Mbps,高速模式速度高达480Mbps,且相对于工程运用广泛的CYPRESS公司的CY68013等USB接口芯片,有着无需单独开发固件、更改驱动程序的优点,具有模式配置灵

## 产品特写 Product Feature

活,开发周期少等特点<sup>[2]</sup>;上位机 采用 VB 编写,为减小波形绘制的延 时,没有采用 Line 函数,而采用工业 IOCOMP 控件。使用工业控件进行波 形绘制的优点是美观功能强大,执行 效率高。

1、多通道的模拟信号采集电路 设计

根据高速遥测采编器的任务设计要求,需要实现 32 路飞行器状态传感器的模拟信号,单路模拟信号的最大频率为 20.46kHz,电压范围  $0\sim5V$ 。根据香浓定理,如果不失真地采样信号时,要求 ADC 的采样率 $\geq 2f_h$ (实际设计时一般至少  $5f_h$ )。如果使用一片 ADC,要求 ADC 芯片的采样率20.46kHz $\times$ 32 $\times$ 2=1.309MHz。本文选用 AD9220,其采样率为 10MHz,分辨率为 12 位,可灵活配置电压输入方式,可接成差分输入或单端输入,内置高性能、低噪声的放大器和可编程基准电压源。

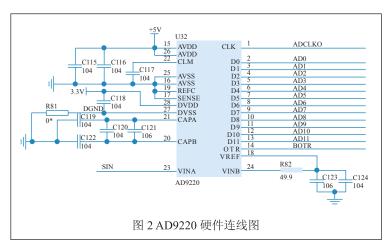

AD9220硬件连线图如图2所示, CLK 是 AD9220 时钟输入引脚, 其  $V_{IH} \ge 3.5$ V, $V_{IL} \le 1.0$ V。因 FPGA 的 I/ O输出电压为 3.3V, 因此 FPGA 的时 钟 ADCLKO 的输出信号经非门驱动 连接至 AD9220 的 CLK。D0 (MSB) ~D11 (LSB) 为输出引脚, OTR 为溢 出引脚, 当输入电压超过量程时 OTR 变成高点平。AD9220的电压输入范 围可以灵活配置。当 SENSE 与 VREF 连接时, 内部基准放大器配置为单增 益模式, VREF输出为1V, 此时输 入电压范围为 0~1V; 当 SENSE 与 REFC 连接时,内部基准放大器配置 为2.5倍增益模式, VREF输出为2.5V, 此时输入电压范围为 0~5V。DVDD

表 1 电极点建立 1LSB 精度的时间常数数量

| 分辨率(位数) | 时间常数数量 =-ln(% 误差 /100) |

|---------|------------------------|

| 6       | 4.16                   |

| 8       | 5.55                   |

| 10      | 6.93                   |

| 12      | 8.32                   |

| 14      | 9.70                   |

为数字输出的参考电压,为了与 FPGA 的 I/O 电压兼容,将 DVDD 连接至  $3.3\mathrm{V}$  电源  $^{[3]}$ 。

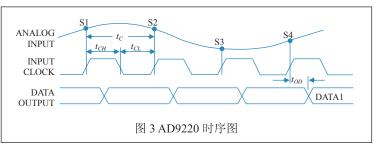

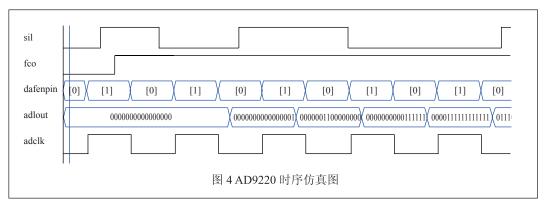

AD9220 的时序简单,采样实现方便,其时序图如图 3 所示。经过三个时钟和延时  $t_{DO}$ ,转换输出。对 AD9220 逻辑控制仿真图如图 4 所示,sil 为输入信号,fco 为转换开始标志,danfenpin 为数据存储标志,当为1时向存储器存储数据,adclk 为 AD 时钟,adlout 为 AD9220 输出数据。

AD9220 为单通道输入,要采集 8 路模拟信号,需要使用模拟开关进行切换。本文选用 ADG715 芯片,其通道数为 16,导通电阻  $R_{ON}$  为  $2.5\Omega$ ,  $C_D$  为 100pA,开关时间为 25ns。根据参考文献 [4],模拟开关建立时间 = 开关切换时间 +  $(R_{ON}C_D \times$  时间常数)。对于时间常数来说,参考文献 [5] 给出了单极点建立时间 1LSB 精度需要时间常数的经验值 (如表 1),那么:

(1)

$$T_{SettleMUX} = T_{Transition} + \frac{R_{ON} \times R_{LOAD}}{R_{ON} + R_{LOAD}} (C_D + C_{LOAD}) \times$$

时间常数

对于 ADC 采样率的 12 位分辨率对应的时间常数数量为 8.32。根据公式求得  $T_{SenteMUX}$  =4.32μs。模拟开关对应的采样率为  $f_s = \frac{1}{T_{SentleMUX} \times \text{通道数}} = 1/(4.32 \mu \text{s} \times 8) \approx 2.89 \text{MHz}$ ,符合本系统的设计要求 [5]。

2、数字滤波设计与 FPGA实现

信号进行了预处理的有 源一阶滤波后,噪声并不能 滤除干净。为了配置的灵活 性,本文在对ADC输出的量 化信号进行数字滤波。数字滤 波器使用较多的 FIR (有限脉 冲响应)和IIR(无限脉冲响 应)两种滤波器。FIR滤波器 较 IIR 滤波器有着较严格的线 性相位特性,而 IIR 滤波器具 有较高的滤波效率和较少的 硬件资源,但实现相对复杂[6]。 本文将使用 FIR 滤波器。怎 么配置滤波器参数才能进行 有效的信号滤波,这就需要进 行设计前的仿真。本文通过的 实测数据,发现信号中噪声的 主要形式是白噪声。

设置好采样频率 $f_s$ ,过渡带 [21kHz 30kHz] 和纹波,先通过凯塞窗获得滤波阶数N,确定阶数N再通过firpm 函数设置最优滤波器,通过 round( $h_pm/max(abs(h_pm))*(2^11-1))$  进行 12 位量化。

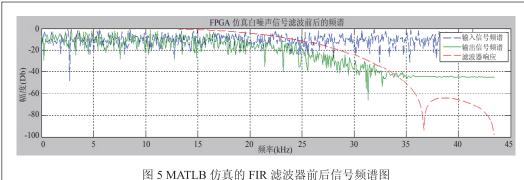

MATLAB 的滤波器设计程序,得到的滤波器进行信号仿真,其仿真结果如图 5 所示。可以看出信号在21kHz 开始衰减,衰减区间大约在 21kHz~30kHz,得到的量化的滤波系数序列 h(n)。直接型的 FIR 滤波输入/输出关系为:

$$y(n) = \sum_{k=0}^{N-1} h(k)[x(n-k) + x(n-N+1+k)] + h((N-1)/2)x(n-(N-1)/2)$$

(2)

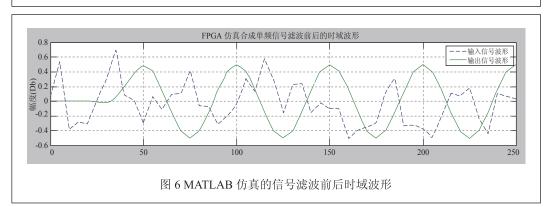

根据式(2)得到滤波结果,如图6所示。FPGA

## 产品特写 Product Feature

中有集成的 FIR 滤波器 IP 核,因此通过 FIR 滤波器的 参数指标:滤波阶数、采样频率 $f_s$ 、阻带边缘频率、通带边缘频率、最小阻带衰减 $A_s$ 、输入、输出数据宽度,生成 FIR 滤波器模块,实例化后调用即可。

MATLAB 设计滤波器程序如下:

fs: % 采样频率

fc=[fc1 fc2]: % 过渡带

mag=[01]: % 窗函数的理想滤波器幅度

dev=[0.001 0.01]: % 纹波

[n, wn, beta, ftype]=kaiserord(fc, mag, dev, fs) % 获取凯 塞窗泰数

fpm=[0 fc(1)\*2/fs fc(2)\*2/fs 1]: %firpm 函数的频段向量 magpm=[0 0 1 1]: %firpm 函数的幅值向量 % 设计最优滤波器

h\_pm=firpm(n, fpm, magpm): % 滤波系数进行量化

h\_pm12=round(h\_pm/max(abs(h\_pm))\*(2^11-1)):%12bit

量化

#### 3、USB接口电路设计

由于模拟信号总的最大采样率为 1.309Msps, 精度为12位,通过USB上传数据时速率应大于 2.618Mbps的速率才能满足信号传输要求。本设计采用 FTDI 公司的第 6 代产品 FT232H, 其异步 FIFO 模式下的传输速率为 8Mbps,满足设计要求。无需单独开发固件和驱动程序,只需在 FTDI 官网上下载。因需要将 232H 配置为异步 FIFO 模式,需要 EEPROM,这

里选用 93LC56。该 EEPROM 的作用是配置 USB 芯片的 VID、PID 和 OEM 信息,此外 FT232H 芯片的工作模式与 ACBUS 接口功能也是通过该芯片配置完成。配置后通过 FT\_PROG 软件烧入到 EEPROM 中。FT232H 的驱动程序有两种: VCP 和 D2XX。其中VCP 驱动是将 FT232H 的 USB 接口虚拟成串口,而D2XX 是驱动 USB 通信接口 [4]。

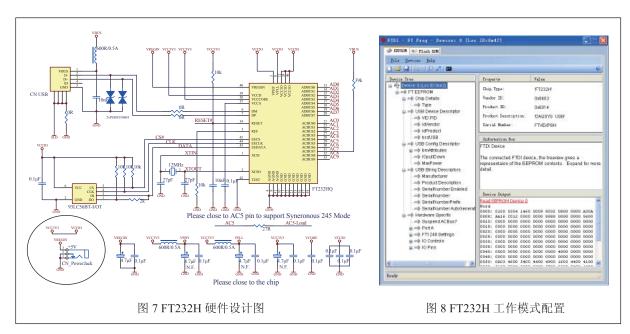

FT232H 硬件设计图如图 7 所示。该芯片使用总线供电方式,即电源引脚 VREGIN 接至 USB 接口的 VCC。当采用总线供电方式时,VCCCORE 引脚是输出引脚,输出电压为 1.8V。为减少信号干扰,VPHY 引脚与 VPLL 引脚接至 3.3V 电压时采用 LC 低通滤波。引脚 ADBUS0~ADBUS7 是 I/O 数据接口,在异步FIFO 模式下 ACBUS0~ACBUS4 分别配置为读准备信号(RXF#)、写准备信号(TXE#)、读信号(RD#)、写信号(WR#)和睡眠唤醒信号(SIMU)。其时序控制图可参见参考文献 [4]。FT232H 安装驱动后,需要配置工作模式。配置工具是 FT\_Prog,配置 VID和 PID 分别为 0403、6014,产品描述为 DAQSYS\_USB,工作模式设置为 245FIFO 模式,并配置响应的 I/O 功能,配置的界面如图 8 所示。

### 三、基于 IOCOMP 控件的上位机设计

#### 1、USB 读写操作

FT232H 完成硬件设计后,需要对软件进行开发。 软件包括驱动、固件和上位机等。其中驱动和固件 FTDI 公司已经编写后,不需用户单独开发,而上位机 需要用户自行完成。

上位机实现对 USB 设备的读写操作是通过 FTDI 的动态链接库 FTD2XX.DLL。主要应用的如下几种函数.

- (1) FT\_OpenEx: 打开一个 USB 设备,并返回 对应的句柄用于其他函数的使用;

- (2) FT\_Read: 读取 USB 设备数据,成功返回 FT OK 状态值;

- (3) FT\_Write: 向 USB 设备下发数据,成功返回 FT OK 状态值;

表 2 上位机下发命令集

| 指令响应 | USB D0~D7 | 功能说明          |

|------|-----------|---------------|

| 启动测试 | EB 90 F1  | 启动实时监测并记录     |

| 自检测试 | EB 90 F2  | 远程回读记录器中数据    |

| 停止测试 | EB 90 F3  | 选择递增数作为数字量信号源 |

- (4) FT\_Purge: 清理指定 USB 设备的发送和接收缓冲区:

- (5) FT Close: 关闭设备,释放句柄<sup>[4]</sup>。

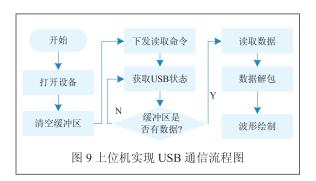

上位机实现 USB 通信流程图如图 9 所示。首先打开设备,清空缓冲区,再下发读取数据命令,下位机接收命令后开始向上位机上传数据,上位机通过获取 USB 设备状态判断缓冲区是否有数据,如果有数据则进行 USB 读取操作。数据读取后按照一定帧格式对数据的解包,最后绘制波形并界面显示。

上位机与 USB 下位机的命令表如表 2 所示。EB 90 为命令标识字节。

#### 2、波形显示

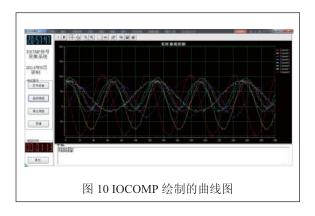

使用 VB 进行波形显示时,通常都会使用 VB 自带 Line 函数。但对于高速的数据采集,对上位机对数据的处理时延有着严格要求。而 Line 函数在大数据的显示下不具优势,时延达百毫秒,这样影响系统整体的运行速率。针对上述问题,本设计采用工业控件IOCOMP,其精美的画面和功能强大胜过 VB 自带绘图函数与 API 函数,试验证明在绘制数万个点时,其延时是 Line 函数的 1/12。

IOCOMP 控件是第三方控件,应用于科学、工程、医疗、石油、天然气、半导体、工厂自动化、航空航天、军事、电信、建筑等领域<sup>[7]</sup>。支持 VB.Net, C#.Net, C++.Net 等平台。本设计采用 IOCOMP 控件的 ipotXY 组件。上位机采集 6 路正弦信号绘制的曲线如图 10 所示。需要注意的是各路信号的点数必须一致。

调用 IOCOMP 控件时,通过 iPlotX1.AddChannel 函 数 增 加 通 道 数,iPlotX1.XAxis(0).Span,iPlotX1.YAxis(0).MIN,iPlotX1.YAxis(0).MIN 分别设置 X 轴和 Y 轴的量程,最后通过iPlotX1.Channel(0).AddXY i, AsyData(i) 绘制曲线。

#### 四、总结

本系统实现 32 路飞行器环境参数的采集,已经作为地面遥测采集设备投入实际使用。本系统也可作为一种通用型采集设备,可实现 0~5V 电压信号的采集与显示。

## 产品特写 Product Feature

#### 参考文献

- [1] 周治良, 刘俊, 张斌珍. 基于 FPGA 及 FLASH 的数据采集存储系统设计 [J]. 微计算机信息,2007,23(3):91-92.

- [2] 杨涛. 高速高精度数据采集系统的研制 [D]. 四川: 电子科技大学, 2004.

- [3] 陈淑芳. 一种高精度数据采集系统模拟信号调理电路的设计 [J]. 长沙铁道学院学报,2008,9(1):215-216.

- [4] Future technology Devices International Ltd., FT232H Signal Channel Hispeed USB to Multipurpose UART/FIFO ICDatasheet[Z]. 2010.

- [5] 李莹, 苏淑靖. 一种高精度多通道数据采集存储电路的设计 [J]. 电视技术, 2013, 37(19): 91-95.

- [6] 郭铮, 刘文怡, 冯妮. 基于 FPGA 多通道高速数据采集存储器设计 [J]. 电视技术, 2012, 36(7): 56-57.

- [7] 刘东,郑恩让,马令坤.基于 FPGA 的 AD73360 数据采集方法 [J]. 计算机测量与控制,2010.18(1):223-225.

# Design of a multi-channel high-speed telemetry editorial

LI Xiao-hong

(Department of Electronic Engineering, Taiyuan Institute of Technology, Taiyuan 030051, China)

Abstract: In this paper, a high-speed multi-channel telemetry editorial is designed, which is used for signal acquisition and real-time display of 32-channel analogue

data of complex environmental parameters in aircrafts. The system adopts one-ADC Time Division Multiplex Access (TDMA) to collect data, digital FIR filter to eliminate white noise, an AD9220 as A/D converter with maximum sampling rate of 10Msps, and USB interface chip FT232H to complete communication with host computer with highest transmission rate of asynchronous FIFO mode up to 8Mbps. Being practical for high-speed data acquisition systems, industry IOCOMP control is used to draw real-time curve quickly instead of Line function for avoiding time-delay. This solution can be used as a general-purpose data acquisition system for different sampling requirements.

Keywords: editorial control; FIR filter; IOCOMP control; AD9220; FT232H

#### 作者简介

李晓红,太原工业学院,助教,硕士。研究方向:信 号与系统

通信地址: 山西省太原市尖草坪区迎新街太原工业学院电子工程系

邮编: 030008 E-mail: xh li86@163.com